Public info about the author: Ishtiaq

- Profile

-

The first phase locked loop was proposed by a French scientist de Bellescize in 1932. Basic idea of working: reduction of phase difference between a locally generated signal and a reference signal by using feedback. A Phase Locked Loop (PLL) circuit synchronizes to an input waveform within a selected frequency range, returning an output voltage proportional to variations in the input frequency. Used to generate stable output frequency signals from a fixed low-frequency signal.

- Free

- Intermediate

- 11-20

- Other

- Simplorer 11.0

- No

-

A phase-locked loop is a feedback system combining a voltage controlled oscillator (VCO) and a phase comparator so connected that the oscillator maintains a constant phase angle relative to a reference signal. Phase-locked loops can be used, for example, to generate stable output high frequency signals from a fixed low-frequency signal. A phase locked loop, PLL, is basically of form of servo loop. Although a PLL performs its actions on a radio frequency signal, all the basic criteria for loop stability and other parameters are the same.

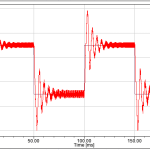

The basic phase locked loop is connected as shown in the diagram below. The reference signal and the signal from the voltage controlled oscillator are connected into the phase detector. The output from the phase detector is passed through the loop filter and then applied to the voltage controlled oscillator. The Voltage Controlled Oscillator, VCO, within the PLL produces a signal which enters the phase detector. Here the phase of the signals from the VCO and the incoming reference signal are compared and a resulting difference or error voltage is produced. This corresponds to the phase difference between the two signals.

The error signal from the phase detector passes through a low pass filter which governs many of the properties of the loop and removes any high frequency elements on the signal. Once through the filter the error signal is applied to the control terminal of the VCO as its tuning voltage. The sense of any change in this voltage is such that it tries to reduce the phase difference and hence the frequency between the two signals. Initially the loop will be out of lock, and the error voltage will pull the frequency of the VCO towards that of the reference, until it cannot reduce the error any further and the loop is locked. When the PLL, phase locked loop, is in lock a steady state error voltage is produced. By using an amplifier between the phase detector and the VCO, the actual error between the signals can be reduced to very small levels. However some voltage must always be present at the control terminal of the VCO as this is what puts onto the correct frequency. The fact that a steady error voltage is present means that the phase difference between the reference signal and the VCO is not changing. As the phase between these two signals is not changing means that the two signals are on exactly the same frequency.The phase locked loop, PLL, is one of the most versatile building blocks in radio frequency electronics today. Whilst it was not widely used for many years, the advent of the IC meant that phase locked loop and synthesizer chips became widely available. This made them cheap to use and their advantages could be exploited to the full.

-