Public info about the author: rwender

- Profile

- Configurable mixed-signal ViaASIC evangelist.

-

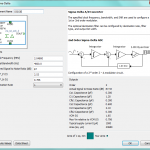

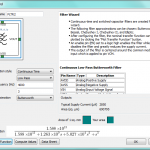

A first order sigma-delta ADC created with a ViaDesigner Sigma-Delta Modulator wizard. The 1-bit digital output is then passed to a simple ‘positive’ or ‘negative’ output DAC. The DAC output is then filtered with a continuous time filter to remove the high frequency oversampling noise. The output waveform is a reconstructed version of the input waveform.

- Free

- Simple

- <10

- ViaDesigner

- 2012.2+

- Yes

-

This simple project demonstrates the creation of a complex mixed signal function such as a Sigma-Delta ADC utilizing ViaDesigner's design wizards. The design contains a SD_ADC Wizard element that has been configured as a first order sigma delta modulator. The output of the SD modulator is a 1-bit digital stream with a "ones density" representing the magnitude of the analog waveform. The closer the analog waveform is to the positive reference of the modulator (VREFP) the more ones in the output of the bitstream. When the analog waveform approaches the negative reference of the modulator (VREFN) the digital bitstream contains more zeroes. When the analog waveform is between the references the digital output's ones density is proportional to the magnitude of the analog waveform. Due to the oversampling nature of the sigma delta modulator, the output bit stream contains shifted or shaped noise. This noise is high frequency in nature and can easily be filtered out with a simplified (low order) continuous time filter. The design passes the digital bit stream to a simplified 1-bit DAC consisting of two switches. When the digital bit stream is a '1' the DAC switches out the positive reference voltage. When the bit stream is a '0' the DAC outputs the negative reference. The design contains a Filter Wizard block that implements a continuous time filter to remove the high frequency over sampling clock noise. The resultant analog output waveform appears as a time delayed version of the analog input 'vin'. The mixed signal design elements are modeled with VHDL-AMS models. The VHDL-AMS models run significantly faster than SPICE models. A complete simulation of the Sigma Delta Modulator and reconstruction filter can be completed in a under a minute.

-