Description

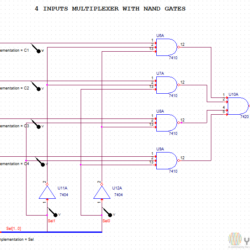

The CMOS implementation of a DPLL using the Phase Frequency Detector with this configuration is preferred over the tri-state output, because of the better immunity to power supply variation. This SPICE simulation shows how too small values of the loop damping factor affects the loop, creating trouble locking.

Reviews

There are no reviews yet.