Description

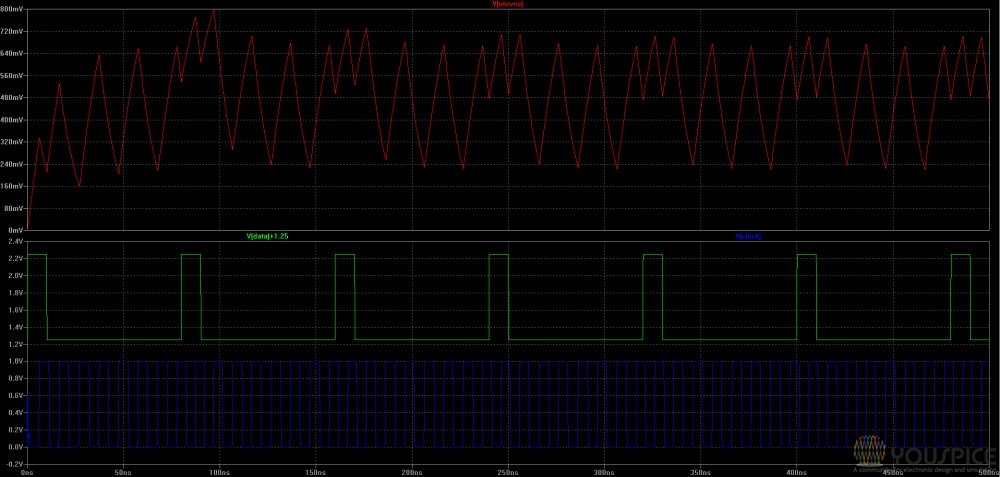

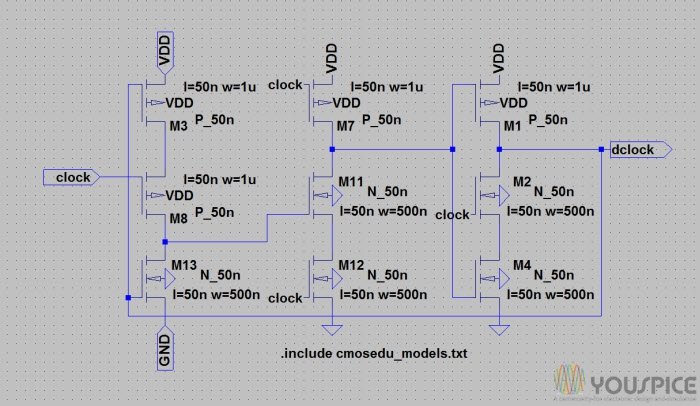

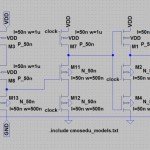

SPICE simulation of a DPLL with XOR phase detector. This is a fundamental circuit in the transmission of digital data. Before the transmission, data is loaded into a shift register and shifted out sequentially, using a system clock. At the receiving side, the receiver amplifies and eventually change the data back into digital logic levels. To shift the data back into a shift register, a clock signal is necessary. The DPLL generates a clock signal locked with the incoming signal, and clocks the shift register for recovering transmitted data.

Reviews

There are no reviews yet.