Description

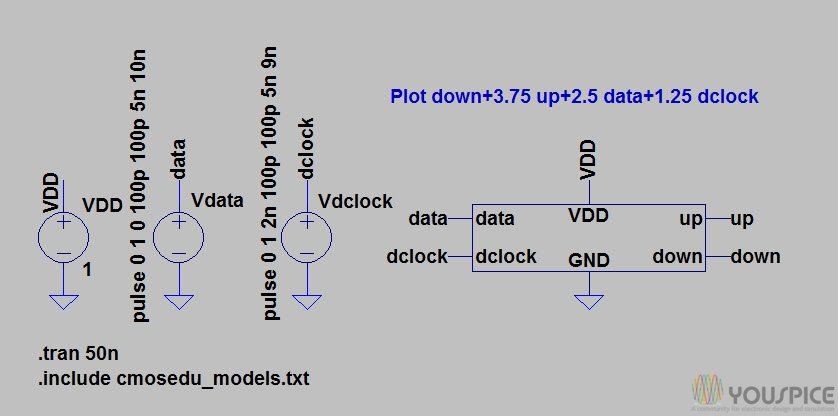

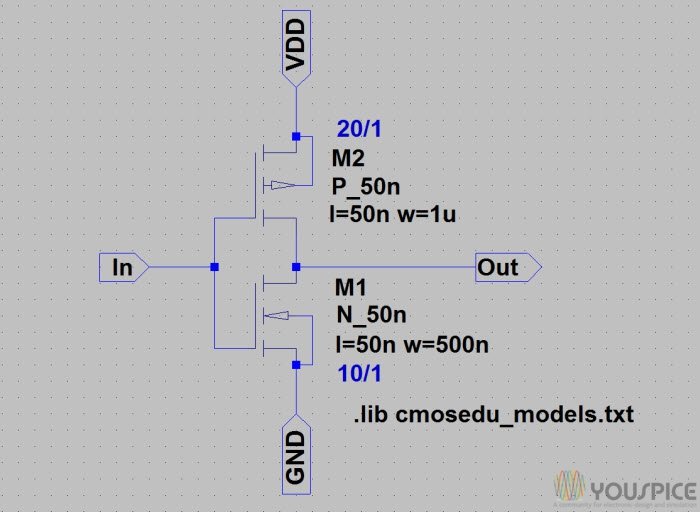

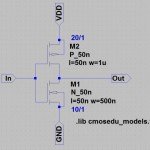

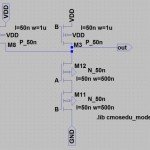

This is a tri-state output circuit with outputs that can assume logic state ‘1’, ‘0’ and High impedance state, electrically isolated from the bus. This phase detector can be used in DPLL in place of XOR phase detector. It’s implemented with inverters and nand gates. The SPICE circuit simulation shows that when the clock is lagging the data, the output of PFD is the up pulse indicating the dclock needs to speed up, when the data is lagging dclock the down pulse goes high indicating dclock should slow down.

Reviews

There are no reviews yet.