In this article, we will explore the ESD Generator SPICE Simulation using an LTSpice model, shedding light on how this powerful tool can help analyze and enhance ESD protection strategies in electronic circuits.

ESD generator, also known as an “Electrostatic Discharge Generator,” is a device used in industrial and testing environments to simulate controlled and repeatable electrostatic discharges (ESD), which are sudden and brief electric currents that can damage or disrupt other electronic equipment. These generators are employed to test the resistance of electronic devices and circuits to simulated electrostatic discharges, assessing how these devices react and whether they are adequately protected against ESD-induced damage.

ESD generators can simulate different types of ESD pulses, such as those defined by various standards and applications. For example, some ESD generators can produce pulses that mimic the human body model (HBM), the machine model (MM), or the charged device model (CDM) of ESD. Some ESD generators can also produce pulses that comply with the requirements of the International Electrotechnical Commission (IEC) 61000-4-2 standard, which specifies the test levels and methods for evaluating the ESD immunity of electrical and electronic equipment.

To take your first steps with LTSpice simulation software, you can read this article.

Università Politecnica delle Marche, Ancona, Italy.

by

Ing. Luca Buccolini

A SIMPLE SPICE ESD GENERATOR CIRCUIT BASED ON IEC61000-4-2 STANDARD

WHAT IS ESD?

Static charge is an unbalanced electrical charge at rest. Typically, it is created by insulator surfaces rubbing together or pulling apart. One surface gains electrons, while the other surface loses electrons. This results in an unbalanced electrical condition known as static charge.

When a static charge moves from one surface to another, it becomes ESD. ESD is a miniature lightning bolt of charge that moves between two surfaces that have different potentials. It can occur only when the voltage differential between the two surfaces is sufficiently high to break down the dielectric strength of the medium separating the two surfaces.

When a static charge moves, it becomes a current that damages or destroys gate oxide, metallization, and junctions. ESD can occur in any one of four different ways: a charged body can touch an IC, a charged IC can touch a grounded surface, a charged machine can touch an IC, or an electrostatic field can induce a voltage across a dielectric sufficient to break it down

ESD STRESS MODELS

ESD can have serious detrimental effects on all semiconductor ICs and the system that contains them. Standards are developed to enhance the quality and reliability of ICs by ensuring all devices employed have undergone proper ESD design and testing, thereby, minimizing the detrimental effects of ESD. Three major stress methods are widely used in the industry today to describe uniform methods for establishing ESD withstand thresholds (highest passing level).

HUMAN BODY MODEL (HBM)

The HBM is a component level stress developed to simulate the action of a human body discharging accumulated static charge through a device to ground, and employs a series RC network consisting of a 100 pF capacitor and a 1500 Ohm resistor.

CHARGED DEVICE MODEL (CDM)

The CDM is a component level stress that simulates charging and discharging events that occur in production equipment and processes. Potential for CDM ESD events occur when there is metal-to-metal contact in manufacturing.

SYSTEM LEVEL ESD (IEC 61000-4-2)

The IEC system level ESD is a widely accepted European standard that defines an ESD event that is meant to be tested on actual end equipment to simulate a charged person or object discharging into electronic systems. The IEC standard defines an ESD stress that is much stronger than the component level ESD stresses defined by HBM and CDM.

The engineer must design following IEC 61000-4-2 standard to be able to declare the conformity CE (“Conformité Européenne”).

The ESD generator circuit realized in this work is compliant with ESD generator used in EMC laboratories to perform CE-conformity tests, thus a SPICE simulation can be used to test ESD-immunity solutions before circuit production.

IEC 61000-4-2 WAVEFORM CHARACTERISTICS

The standard accurately describe the characteristics and performances of the ESD generator as well as the current waveform parameters.

The ESD phenomenon is a very short but very strong current transient and is represented in Figure 1.

Figure 1. 61000-4-2 ideal contact ESD waveform at 4kV

This pulse is divided into two parts: The first peak, known as the “Initial Peak”, is caused by the discharge of the arm, and generates the maximum current. The second peak is caused by the discharge of the body. The rise time of the initial peak is between 0.6 ns and 1 ns, and its amplitude depends on the charging voltage of the ESD simulator.

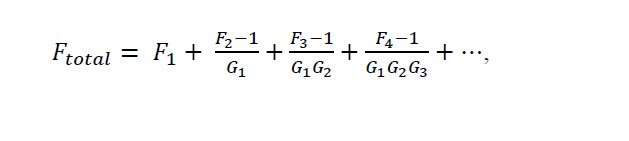

The standard describe a formula and the mains current level of the waveform for different test level.

Table 1 contact discharge current waveform parameters

Even though the IEC 61000-4-2 [2] include a simplified circuit of ESD generator, it is incompatible with the discharge current equation descripted in the standard and the waveform shown in Figure 1. A PSpice software simulation can prove this.

THE BASIC ESD GENERATOR MODEL

In order to run ESD stress simulation, an ESD-generator model was built. This can help engineers to test different solutions in a SPICE simulator to overcome strength over-voltages before realizing PCB circuit and test it against ESD.

The objective is to generate an ESD pulse that accurately corresponds to the current stress waveforms at various stress levels in accordance with the IEC 61000-4-2 specification.

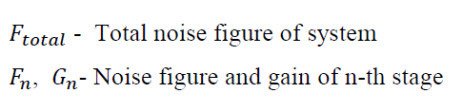

The ESD can be simulated by two parallel R, L, C circuits with charged capacitors. The generator equivalent circuit is shown in Figure 2.

Here the standardized network elements of the ESD-generator are represented by R1 (330ohm) and C1 (150pF). The inductor L1 is considered to be the obligatory ground strap with the length of about 2 m. Physically the first peak of the pulse is shaped by additional lumped and parasitic elements around and in the tip of the ESD-generator [5].

Note that the values of R, L, and C for both branches are tweaked to correctly represent standard IEC stress waveform; “.ic V(c1)=4kV V(c2)=4kV” refers to the initial condition of the voltage on the capacitors for a 4kV zap.

Figure 2 The general equivalent circuit of basic IEC61000-4-2 generator model