LTspice Modeling of Universal Operational Amplifier

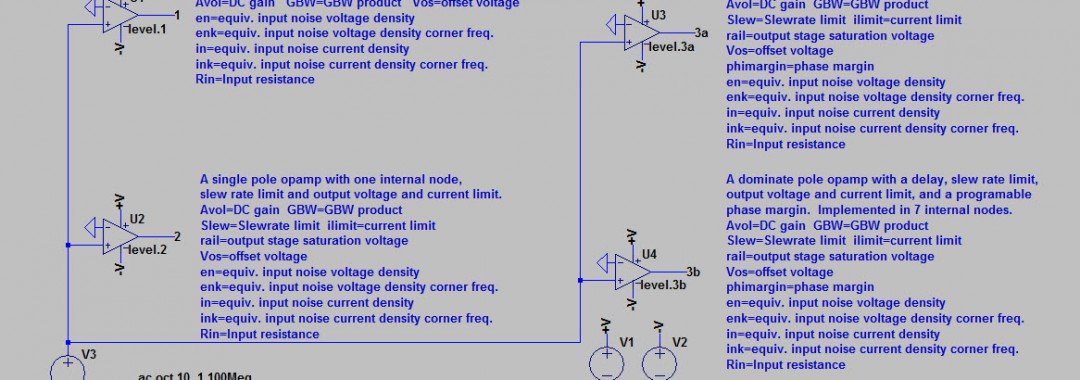

LTspice model with 4 levels of accuracy of the description of an operational amplifier.The first level models a linear single pole opamp with no slew rate or output voltage range limit. The second level introduces the slew rate and output voltage and current limit. The third level is a two pole with programable phase margin […]